## Microwave Resistivity of Thermally Oxidized High Resistivity Silicon Wafers

JAROSłAW JUDEK,  $^1$  MARIUSZ ZDROJEK,  $^{1,4}$  DARIUSZ SZMIGIEL,  $^2$  and JERZY KRUPKA  $^3$

1.—Faculty of Physics, Warsaw University of Technology, Koszykowa 75, 00-662 Warsaw, Poland. 2.—Institute of Electron Technology, al. Lotnikow 32/46, 02-668 Warsaw, Poland. 3.—Institute of Microelectronics and Optoelectronics, Warsaw University of Technology, Koszykowa 75, 00-662 Warsaw, Poland. 4.—e-mail: zdrojek@if.pw.edu.pl

We used a microwave dielectric resonator to study how the process of thermal oxidation of high resistivity silicon wafers reduces the wafer microwave resistivity. Measurements were performed before surface thermal oxidation, after the oxidation, and after wet oxide removal. We show that the process of oxide growth decreases the microwave resistivity of the wafer from approximately 20 k $\Omega$  cm to as low as 400  $\Omega$  cm (typically to 1–2 k $\Omega$  cm), depending on the dielectric layer thickness and the growth process conditions. After the wet removal of SiO<sub>2</sub>, the resistivity of the wafers increased, but it did not reach the initial value.

**Key words:** High resistivity silicon, microwave resistivity, thermal oxidation

High resistivity silicon (HRS,  $\rho \ge 1 \text{ k}\Omega \text{ cm}$ ) substrates are widely applied semiconductors in microwave and terahertz technology. HRS is used, e.g., as a base material for silicon monolithic microwave integrated circuits (Si MMICs) or, especially in recent years, as a convenient substrate for radiofrequency devices, 1-3 including those that are emerging and based on novel low-dimensional materials, such as ultrafast graphene photodetectors<sup>4</sup> or graphene coplanar waveguides (CPW).<sup>5</sup> The advantages of using HRS wafers are their easy accessibility, relatively low price, and low level of high-frequency dissipation losses, which are important factors for operating RF devices and for propagating the microwave signal. The main disadvantage of using HRS substrates is a bias-dependent leakage current effect, which could lead to unintentional shortening of the designed circuitry through the poorly conducting substrate. To remove this obstacle, the surface of the HRS wafer can be oxidized to produce a dielectric layer. Unfortunately, the process of oxide growth can significantly reduce the sheet resistance of the wafer, as shown

by Reyes, Wu, and Gamble. Examining the problem of microwave signal losses in CPW fabricated on high resistivity silicon substrates, they found that the microwave signal losses increased from approximately 2 dB/cm up to 18 dB/cm at 30 GHz<sup>7,8</sup> when the surface of HRS was covered with the silicon dioxide dielectric layer. This result was an important finding because such high dissipation losses could make MMICs on SiO<sub>2</sub>/HRS substrates useless, despite the significant reduction in the leakage currents. The increased dissipation was explained by the emergence of surface states that trap the inversion/accumulation charges and prevent them from going to the conduction/valence band, thereby lowering the effective surface resistivity of the Si covered with SiO<sub>2</sub>. Solutions that have been considered, so far, when attempting to solve the problem of excessively low sheet resistance include selective etching of the SiO<sub>2</sub> layer or deposition of a polycrystalline silicon buffer layer between the Si and the SiO<sub>2</sub>.

In this paper, we bring important evidence on the influence of the SiO<sub>2</sub> thermal growth process on the HRS resistivity. We show that the process significantly lowers the microwave resistivity of the HRS wafer and that the value of the resistivity is not reversible after the oxide removal. In order to show

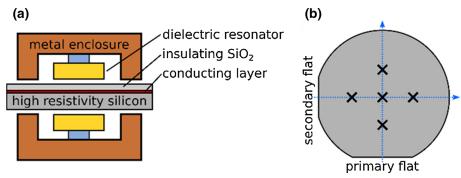

Fig. 1. (a) Schematic of the experimental setup (split-post microwave resonator operating at 4.5 GHz), (b) the locations on the silicon wafer where point measurements were performed ("x" symbol). Blue dotted lines indicate the scan directions (Color figure online).

this, we used the microwave cavity technique<sup>9</sup> as a research tool because it has the following properties: (1) it is a contactless technique that does not require a fabrication process, (2) it allows wafer mapping, (3) it allows measurements at different stages of the silicon wafer production process, and (4) it allows probing of the resistivity of a conducting layer sandwiched between two insulating/poorly conducting layers, which is not possible in the case, e.g., of the four-point probe method. Measurements were performed before surface oxidation, after the oxidation, and after oxide removal to determine whether the emergence of a conducting layer at the  $Si/SiO_2$ interface is the only reason for the resistivity decrease and to what extent the wafer resistivity can be restored.

High resistivity silicon wafers (diameter 4", thickness 525  $\mu m$ , orientation 100, boron doping, resistivity  $\geq \! 10~k\Omega$  cm, one side polished) were produced by Topsil Semiconductor Materials S.A. via the flat zone method. The resistivities of pristine wafers were determined using a microwave split-post resonator operating at approximately 4.5 GHz just before the process of oxide growth. In order to exclude place-dependent results, the measurements were performed at five points on the wafer (see Fig. 1). We emphasize that no significant differences among these points were observed, and the averaged results, which confirm the information given by the producer, are presented in Table I.

Next, silicon wafers were oxidized in a Thermco horizontal furnace. Prior to the oxidation process, the wafers were cleaned in RCA standard solutions. Three different oxidation process recipes were used to obtain high-quality silicon oxide layers of a required thickness within a reasonable period of time:

- Recipe 1 (gives  $SiO_2$  layer with thickness of 10 nm): (1) heating up to  $950^{\circ}C$  in  $N_2/O_2$  (20:1); (2) temperature stabilization in  $N_2$ ; (3) oxidation in  $N_2/O_2$  (3.3:1); (4)  $N_2$  purge; (5) cooling down to  $800^{\circ}C$  in  $N_2$ .

- Recipe 2 (gives SiO<sub>2</sub> layer with thickness of 20– 100 nm): (1) heating up to 950°C in N<sub>2</sub>/O<sub>2</sub> (20:1);

- (2) temperature stabilization and pre-oxidation in  $N_2/O_2$  (3.3:1); (3) oxidation in dry  $O_2;$  (4)  $N_2$  purge; (5) cooling down to  $800^{\circ}C$  in  $N_2.$

- Recipe 3 (gives SiO<sub>2</sub> layer with thickness of 300 nm): (1) heating up to 950°C in N<sub>2</sub>/O<sub>2</sub> (20:1); (2) temperature stabilization and pre-oxidation N<sub>2</sub>/O<sub>2</sub> (3.3:1); (3) oxidation in dry O<sub>2</sub>; (4) oxidation in O<sub>2</sub> + H<sub>2</sub>, (5) oxidation in dry O<sub>2</sub>; (6) N<sub>2</sub> purge; (7) cooling down to 800°C in N<sub>2</sub>.

The oxide thickness was measured using spectroscopic ellipsometry, which is the most common and widely used approach to determine the precise value of the oxide layer. <sup>10,11</sup> The error in estimation of the oxide thickness is approximately 1 nm. Modeling of an air/SiO<sub>2</sub>/Si structure was used to calculate the thickness of the layer, assuming a Cauchy model for the optical properties of the oxide.

Immediately after the thermal oxidation process, the resistivities of the wafers were determined again using the microwave resonator. The values of the resistivities measured at the center of the wafer are presented in Table I. The following comments should be made regarding the data.

First, it can be clearly seen that after thermal oxidation of HRS wafers, their resistivities significantly decreased (averaged drop in resistivity equals 94%). This observation is consistent with previously published reports<sup>6–8</sup> because the wafer resistivity is directly related to the microwave losses. This can be explained using the definition of the complex relative permittivity, which can be written using following equation:

$$arepsilon_{

m r} = arepsilon_{

m r}' - j arepsilon_{

m r}'' - j rac{\sigma}{\omega arepsilon_0}$$

where  $\varepsilon_0$  is the permittivity of vacuum,  $\varepsilon_r$  is the relative complex permittivity,  $\varepsilon_r'$  is the real part of the relative complex permittivity,  $\varepsilon_r''$  is the imaginary part of the relative complex permittivity,  $\omega$  is the angular frequency, and  $\sigma$  is the material conductivity. From the formula above it can be seen that the imaginary term includes both dielectric losses and losses related to the conductivity.

| Table I. Values for the resistivity | of the HRS wafers before oxide growth, | after oxide growth, and after oxide |

|-------------------------------------|----------------------------------------|-------------------------------------|

| removal                             |                                        |                                     |

| HRS wafer number                   | 1               | 2                 | 3               | 4               | 5               | 6            | 7                 | 8               | 9                | 10        |

|------------------------------------|-----------------|-------------------|-----------------|-----------------|-----------------|--------------|-------------------|-----------------|------------------|-----------|

| Oxide thickness (nm)               | 10 <sup>a</sup> | $20^{\mathrm{b}}$ | 28 <sup>b</sup> | 38 <sup>b</sup> | 50 <sup>b</sup> | $50^{\rm b}$ | $50^{\mathrm{b}}$ | 75 <sup>b</sup> | 103 <sup>b</sup> | $302^{c}$ |

| $\rho_1$ —resistivity before oxide | 23147           | 22646             | 21803           | 22188           | 21649           | 24439        | 22705             | 23471           | 24057            | 21105     |

| growth $(\Omega \text{ cm})$       |                 |                   |                 |                 |                 |              |                   |                 |                  |           |

| $\rho_2$ —resistivity after oxide  | 1401.6          | 617.41            | 1057.9          | 1046.1          | 962.51          | 1023         | 1134.6            | 855.81          | 2246.8           | 2641.4    |

| growth $(\Omega \text{ cm})$       | -93.9%          | -97.3%            | -95.1%          | -95.3%          | -95.5%          | -95.8%       | -95.0%            | -96.3%          | -90.7%           | -87.5%    |

| $\rho_3$ —resistivity after oxide  | 15100           | 7820              | 10900           | 9930            | 5770            | _            | _                 | 4120            | 4910             | 4770      |

| removal (Ω cm)                     | -34.8%          | -65.5%            | -50.0%          | -55.2%          | -73.3%          |              |                   | -82.4%          | -79.6%           | -77.4%    |

| $ ho_{3}/ ho_{2}$                  | 10.8            | 12.7              | 10.3            | 9.49            | 5.99            | -            | -                 | 4.81            | 2.18             | 1.81      |

The percentage resistivity drop is calculated with respect to the initial resistivity value. arcipe 1. recipe 2. recipe 3.

Second, in order to properly interpret the results one needs to remember that in the case of a homogenous material, resistivity is a property of this material. However, in the case of the HRS wafer covered with SiO<sub>2</sub>, one can distinguish at least four layers within the wafer: bulk silicon layer, depletion layer, inversion layer, and dielectric layer. Thus, obtained results of the resistivity need to be treated as the total resistivity of all parallel layers, and its value is dominated by the most conducting layer. For further discussion, please see Ref. 12.

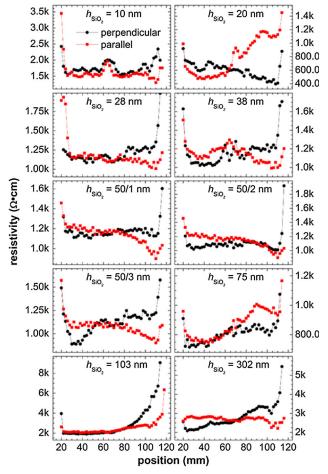

Finally, in contrast to the measurements on pristine wafers, we observed significant differences in the resistivity value that depends on the place on the wafer. Therefore, we constructed a microwave resistivity line scanner based on a microwave splitpost dielectric resonator operating at approximately 14 GHz. Higher resonant frequency implies that the resonator has a reduced active area (change in active area diameter from approximately 15 mm down to 3 mm), which allows scanning at a step size of 2 mm. For each sample, two scans crossing at the center of the wafer were performed—one parallel and one perpendicular to the primary flat (see Fig. 1). The results of the microwave resistivity scans are shown in Fig. 2. The increases in resistivity at the boundaries have no physical meaning and are related to the evacuation of the sample from the active area of the resonator. Significant resistivity variations were observed over the samples. For the 10-nm thick SiO<sub>2</sub> sample, the resistivity increased from an average value of approximately  $1.6 \text{ k}\Omega$  cm to approximately  $2.0 \text{ k}\Omega$  cm in the center of the wafer. For the 20-nm thick SiO<sub>2</sub> sample, the resistivity value changed from approximately  $400~\Omega$  cm to approximately  $1.2~\mathrm{k}\Omega$  cm. For the 28nm thick SiO<sub>2</sub> sample, the resistivity was almost constant, with no distinct features, in contrast to the sample with the 38-nm thick SiO<sub>2</sub> layer, for which a resistivity peak in the center of the wafer can be observed. For the 50-nm thick SiO<sub>2</sub> sample, resistivity changed the from approximately 900  $\Omega$  cm to approximately 1.2 k $\Omega$  cm, whereas for the 75-nm thick SiO<sub>2</sub> sample, the change was from

Fig. 2. Resistivity scans of the HRS wafers covered by  ${\rm SiO_2}$  dielectric layers of different thicknesses. The perpendicular (black plot) and parallel (red plot) directions are fixed with respect to the primary flat. The increase in resistivity at the boundary has no physical meaning and is related to the evacuation of the sample from the active area of the resonator (Color figure online).

approximately 700  $\Omega$  cm to approximately 1 k $\Omega$  cm. For samples with the thickest dielectric layers of 103 nm and 302 nm, the resistivity changed from a relatively high value of approximately 2 k $\Omega$  cm to much greater than 5 k $\Omega$  cm.

According to some works, <sup>6–8</sup> the decrease in the resistivity results in the emergence of surface states that trap the inversion/accumulation charges and prevent them from going to the conduction/valence band, thereby lowering the effective surface resistivity of the Si covered with SiO<sub>2</sub>. Based on this explanation we expect that in our case the observed variation of the resistivity stems from the variations in interface properties, such as charge trap density or the width of the interface, which according to Queirolo<sup>13</sup> depends on oxide thickness.

Next, we verify whether the resistivity of the wafers can be restored upon oxide removal. Thus, just after a complete series of measurements on oxidized samples, silicon dioxide was removed using a very selective etching process performed in BHF (buffered hydrofluoric acid solution). The resistivities of the restored wafers were determined using the microwave split-post resonator at five points (see Fig. 1) and no significant differences were observed among them (similar to the results of the measurements before oxidation and in contrast to the measurements after oxidation). The averaged results are presented in Table I. The resistivity values are significantly lower than the initial ones, particularly for the thickest oxide layers. We also note that the  $\rho_3/\rho_2$  ratio, that illustrates the increase in resistivity due to oxide removal, decreases with increasing oxide thickness. Two possible explanations for the resistivity decrease are: (1) irreversible decrease in the bulk silicon resistivity after high temperature treatment and/or (2) existence of new or preserved surface states after oxide removal. The former one is related to the time of the wafer stay at elevated temperatures, which is higher for thicker oxides, and thus wafers with thicker oxide are longer exposed to potentially harmful conditions. The latter one is related to the width of the interface which is increasing with increasing oxide thickness. Because at the interface the amount of oxygen changes continuously, the BHF etching, which removes oxide, but not silicon might have left some part of the interface meaning rarely distributed oxide atoms in the silicon matrix. Such remains could constitute new or preserved states that are efficient microwave energy dissipation centers. However, more detailed analysis requires further studies (e.g. EELS spectroscopy or SIMS spectrometry), which will allow distinguishing the contribution from surface states and bulk properties.

In summary, we have shown in a straightforward manner that thermal oxidation of the HRS wafer is not a trivial process and can lead to a significant decrease in the mean resistivity. We attribute the resistivity decrease mainly to the emergence of the conductive layer on the  $\mathrm{Si/SiO_2}$  interface. We demonstrate that the conductivity of this layer is inhomogeneous and that oxide removal using buffered hydrofluoric acid solution does not restore the resistivity to its initial value. Our findings could be useful for the semiconductor industry because we demonstrate how to perform fast and robust evaluation of the influence of the oxide growth process on an HRS wafer. These findings could also be useful for designers of RF circuitries on the very popular HRS/SiO $_2$  substrates and for those in the scientific community who are interested in the physical properties of  $\mathrm{Si/SiO_2}$  interfaces.

## **ACKNOWLEDGEMENTS**

This work was supported by the National Centre for Research and Development (Graf-Tech/NCBR/13/20/2013).

## **OPEN ACCESS**

This article is distributed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits unrestricted use, distribution, and reproduction in any medium, provided you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made.

## REFERENCES

- H.S. Gamble, B.M. Armstrong, S.J.N. Mitchell, Y. Wu, V.F. Fusco, and J.A.C. Stewart, *IEEE Microw. Guide Wave Lett.* 10, 395 (1999).

- I. Wolff, Coplanar Microwave Integrated Circuits, (Germany: Wiley, 2006).

- 3. J. Kodate, T. Douseki, T. Tsukahara, T. Okabe, and N. Sato, Jpn. J. Appl. Phys. 8, 5987 (2005).

- F. Xia, T. Mueller, Y.-M. Lin, A. Valdes-Garcia, and P. Avouris, Nat. Nanotech. 4, 839 (2009).

- S. A. Awan, A. Lombardo, A. Colli, G. Privitera, T. Kulmala, J.M. Kivioja, M. Koshino, and A.C. Ferrari, arXiv:1508.04984v1 [cond-mat.mes-hall].

- A.C. Reyes, S.M. El-Ghazaby, S. Dorn, M. Dydyk, D.K. Schroder, and H. Patterson, *IEEE Trans. Microw. Theory Tech.* 43, 2016 (1995).

- Y. Wu, S. Yang, H.S. Gamble, B.M. Armstrong, V.F. Fusco, and J.A.C. Stewart, *IEEE Silicon Monolithic Integrated Circuits in RF Systems* (1998), p. 178.

- H.S. Gamble, B.M. Armstrong, S.J.N. Mitchell, Y. Wu, V.F. Fusco, and J.A.C. Stewart, *IEEE Microw. Guided Wave Lett.* 9, 395 (1999).

- J. Krupka, Meas. Sci. Technol. 24, 062001 (2013).

- S. Charvet, R. Madelon, F. Gourbilleau, and R. Rizk, J. Appl. Phys. 85, 4032 (1999).

- D. Chandler-Horowitz, N.V. Nguyen, and J.R. Ehrstein, AIP Conf. Proc. 683, 326 (2003).

- J. Krupka and J. Judek, *IEEE Trans. Semicond. Manuf.* 4, 530 (2014).

- G. Queirolo, G. Ghidini, L. Meda, C. Signorini, and A. Armigliato, J. Electrochem. Soc. 11, 2381 (1986).